電子工程師必選的EDA軟件 軟件設(shè)計(jì)與開發(fā)全解析

隨著電子技術(shù)飛速發(fā)展,電子設(shè)計(jì)自動化(EDA)軟件已成為電子工程師不可或缺的工具。無論是芯片設(shè)計(jì)、電路仿真還是PCB布局,選擇合適的EDA軟件對提高設(shè)計(jì)效率和產(chǎn)品質(zhì)量至關(guān)重要。以下是電子工程師在軟件設(shè)計(jì)與開發(fā)過程中必選的幾類EDA工具及其代表性軟件。

1. 電路設(shè)計(jì)與仿真軟件

這類軟件用于繪制電路原理圖并進(jìn)行功能仿真,幫助工程師在設(shè)計(jì)早期驗(yàn)證電路性能。

- OrCAD PSpice:由Cadence公司開發(fā),廣泛應(yīng)用于模擬和混合信號電路仿真,提供精確的模型庫和強(qiáng)大的分析功能。

- LTspice:ADI公司推出的免費(fèi)仿真工具,特別適合開關(guān)電源和模擬電路設(shè)計(jì),以其快速仿真速度和易用性著稱。

- NI Multisim:集成了原理圖捕獲和仿真功能,適合教育機(jī)構(gòu)和初學(xué)者,支持從基礎(chǔ)電路到復(fù)雜系統(tǒng)的設(shè)計(jì)。

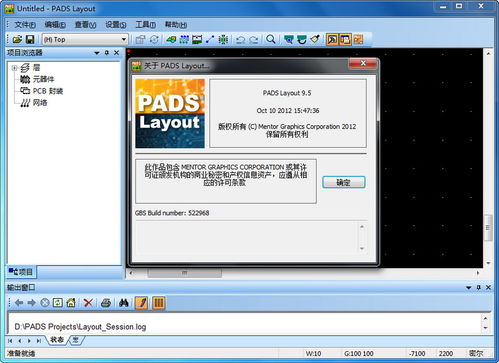

2. PCB設(shè)計(jì)軟件

PCB設(shè)計(jì)是電子產(chǎn)品的核心環(huán)節(jié),需考慮布局、布線和電磁兼容性。

- Altium Designer:功能全面的集成化設(shè)計(jì)環(huán)境,支持從原理圖到PCB布局的全流程,深受中小企業(yè)和獨(dú)立工程師青睞。

- Cadence Allegro:適用于高性能、高密度PCB設(shè)計(jì),在通信和計(jì)算機(jī)行業(yè)廣泛應(yīng)用,提供先進(jìn)的約束管理和信號完整性分析。

- KiCad:開源免費(fèi)的PCB設(shè)計(jì)工具,包含原理圖編輯、PCB布局和3D查看功能,適合預(yù)算有限的項(xiàng)目或開源硬件開發(fā)。

3. 集成電路(IC)設(shè)計(jì)軟件

對于芯片設(shè)計(jì)工程師,IC設(shè)計(jì)工具涵蓋從RTL編碼到物理實(shí)現(xiàn)的各個環(huán)節(jié)。

- Synopsys Design Compiler:邏輯綜合工具的標(biāo)準(zhǔn),用于將硬件描述語言(如Verilog、VHDL)轉(zhuǎn)換為門級網(wǎng)表。

- Cadence Virtuoso:提供完整的模擬/混合信號IC設(shè)計(jì)平臺,支持定制版圖設(shè)計(jì)和仿真驗(yàn)證。

- Mentor Graphics ModelSim(現(xiàn)為Siemens EDA產(chǎn)品):強(qiáng)大的HDL仿真工具,用于數(shù)字電路的功能驗(yàn)證和調(diào)試。

4. 系統(tǒng)級設(shè)計(jì)與驗(yàn)證工具

隨著系統(tǒng)復(fù)雜度的提升,系統(tǒng)級工具能夠處理硬件/軟件協(xié)同設(shè)計(jì)和高級建模。

- MATLAB/Simulink:MathWorks公司的產(chǎn)品,適用于算法開發(fā)、系統(tǒng)建模和仿真,在控制系統(tǒng)和信號處理領(lǐng)域廣泛應(yīng)用。

- SystemVerilog:基于Verilog的硬件驗(yàn)證語言,結(jié)合UVM方法學(xué),成為現(xiàn)代IC驗(yàn)證的主流工具。

- ANSYS HFSS:專業(yè)的電磁仿真軟件,用于分析高頻結(jié)構(gòu)如天線、RF組件,確保信號完整性和EMC合規(guī)。

選擇建議

電子工程師應(yīng)根據(jù)項(xiàng)目需求、預(yù)算和團(tuán)隊(duì)協(xié)作方式選擇合適的EDA軟件。對于初學(xué)者,可從LTspice、KiCad等免費(fèi)工具入手;企業(yè)級項(xiàng)目則需考慮Altium Designer或Cadence套件等商業(yè)軟件。云基EDA平臺(如Cadence Cloud)正逐漸興起,提供靈活的計(jì)算資源和協(xié)作功能,值得關(guān)注。

EDA軟件是電子工程師實(shí)現(xiàn)創(chuàng)新設(shè)計(jì)的基石。通過熟練掌握上述工具,工程師能夠高效完成從概念到產(chǎn)品的全流程開發(fā),推動技術(shù)進(jìn)步。

如若轉(zhuǎn)載,請注明出處:http://www.fdaf.com.cn/product/3.html

更新時(shí)間:2026-02-13 16:56:34